- Home

- Hochschule

-

Studium

- Studienangebote

-

Beratung

- Studienorientierung

- Zentrale Studienberatung

- Studienfachberatung

- Psychosoziale Beratung

- Studienfinanzierungsberatung und Stipendien

- Schreibberatung

- Studieren mit beruflicher Qualifikation

- Studieren mit ausländischen Zeugnissen

- Studieren mit Handicap

- Studieren mit Familie

- Informationen für Schulen

- Auslandsaufenthalt

-

Bewerbung

- Auswahlgrenzen und Vergabeverfahren (NC)

- Bewerbungsportal

- Bewerbung Schritt für Schritt: Von der Bewerbung bis zur Einschreibung

- Bewerbung für ein höheres Fachsemester

- Bewerbung mit beruflicher Qualifikation

- Gasthörerschaft und Zweithörerschaft

- Kontakt Studierendenservice

- Losverfahren

- Promotion

- Sonderanträge

- Studiengang wählen

- Wer kann an der HSBI studieren?

- Studienstart

-

Studium organisieren

- Studierendenservice

- Abschlussunterlagen

- Anerkennung von Leistungen

- Anträge einreichen

- Beurlaubung

- CampusCard

- Einreichung schriftliche Arbeiten

- Erstattung

- Exmatrikulation

- IT-Services

- Online-Serviceportale (LSF/CAT)

- Prüfungsangelegenheiten: Ordnungen, Modulhandbücher

- Rücktritt von einer Modulprüfung

- Rückmeldung

- Semesterbeitrag

- Semesterticket (Studi-Deutschlandticket)

- Semester-, Vorlesungs- und Prüfungszeiten

- Studienbezogene Auslandserfahrung

- Studiengebühren

- Vorlesungsverzeichnis

- Rund ums Studium

- Fachbereiche

- Forschung

- Transfer

- Weiterbildung

- Internationales

- Karriere an der HSBI

Effiziente Ausführung eines Algorithmus zur Objekterkennung auf Edge-Geräten

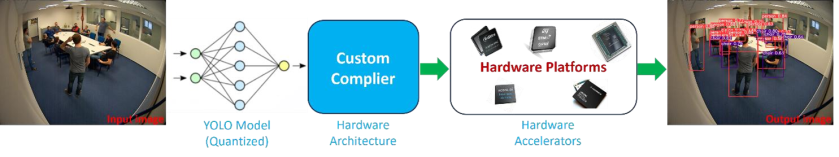

Bild 1: Effiziente Abbildung des YOLO-Vx-Modells auf Randgeräte

Projektübersicht|

Anzahl Studierende |

1 |

|

Art |

Projekt mit externen Partnern |

|

Projektverantwortung |

Prof. Dr.-Ing. habil. Thorsten Jungeblut Dr.-Ing. Qazi Arbab Ahmed |

|

Projektkontext |

Transferprojekt CareTech OWL in Zusammenarbeit mit einem externen Partner, der Steinel GmbH, im Rahmen des Forschungsprojekts CareTech OWL. Eine parallele Beschäftigung als studentische Hilfskraft (WHK) ist möglich. |

Kurzbeschreibung

Für die effiziente Ausführung von KI-Algorithmen haben Techniken wie Föderales Lernen (FL) und Cognitive Edge Computing (CEC) bereits die Last des Trainings und der Inferenz neuronaler Netze von der Cloud an den Ort der Datenentstehung verlagert. Die Partitionierung der Ausführung der Anwendung hat einen erheblichen Einfluss auf die Performanz und Ressourceneffizienz des Gesamtsystems. So kann hier zwischen grundlegend unterschiedlichen Ansätzen der dezentralen Merkmalsextraktion möglichst nah am Sensor mit anschließender Fusion gegenüber der zentralen Verarbeitung in der Cloud unterschieden werden. Der erste Ansatz erfordert leistungsstarke EdgeHardware für die Vorverarbeitung und bietet potenziell Vorteile für hohe Echtzeitanforderungen. Der zweite Ansatz stellt höhere Anforderungen an die Kommunikationsinfrastruktur, ermöglicht aber möglicherweise die Ausführung komplexerer Netzwerke. Das Hauptziel dieses Projekts ist es daher, automatisierte Methoden zur Erforschung des Entwurfsraums geeigneter Kombinationen von KI-basierten Objekterkennungsmethoden und ressourcenbeschränkter Hardware im Hinblick auf HW/KICodesign zu erforschen.

Im Bereich der effizienten Ausführung von KI-Verfahren auf eingebetteten Systemen (Cognitive Edge Computing) wurden in der Vergangenheit große Fortschritte erzielt. Auf allen Ebenen der unterschiedlichen Verarbeitungskonzepte (Cloud, Fog, Edge, Very Edge) in der Produktionskette findet sich eine Vielzahl potenzieller Hardwarearchitekturen und KI-Beschleuniger, die sich in den verfügbaren Systemressourcen (z.B. Leistung oder Stromverbrauch) unterscheiden. Beispiele für relevante Hardwarearchitekturen sind eingebettete Mikrocontroller mit integrierter KI-Beschleunigung, eingebettete GPUs/FPGAs, dedizierte KI-Hardwarebeschleuniger oder High-EndGPUs/FPGAs aus dem HPC-Bereich.

Wir betrachten die gesamte Verarbeitungskette, beginnend mit der sensornahen Vorverarbeitung (very edge), über die Verbindung der Sensorgruppen und ihrer Informationen in der Edge, über lokale dezentrale Cloud-Instanzen (Fog), bis hin zur zentralen Station aller relevanten Informationen (Cloud). Auf jeder Ebene der Verarbeitungskette existieren individuelle Ansätze, um die Ressourceneffizienz von KI-Methoden lokal zu optimieren, z. B. durch Reduzierung der numerischen Präzision (z. B. von 32 auf 16 oder 8 Bit), um eine effizientere Ausführung auf spezialisierter Hardware zu ermöglichen oder den lokalen Speicherplatz zu minimieren. Ziel dieses Projekts ist es, eine optimale Kombination von Hardware und Objekterkennungsalgorithmen (z.B. YOLO) im Rahmen einer ganzheitlichen Entwurfsraumexploration in der Nähe des Sensors zu ermitteln.

AufgabenstellungIn diesem Projekt entwickeln die Studierenden ein Framework für die effiziente Ausführung von KI-basierten Objekterkennungsalgorithmen auf ressourcenbeschränkten Edge-Geräten. Um die nachhaltige Nutzung der entwickelten Methoden und Frameworks durch den Industriepartner zu unterstützen, sollen in diesem Projekt universell einsetzbare Modelle und automatisierte Entwurfswerkzeuge in Form eines Standard-Entwicklungsbaukastens zur Verfügung gestellt werden. Die erste große Herausforderung ist die Komprimierung des neuesten Algorithmus zur Erkennung von Objekten (z. B. YOLO), um die Modellgröße mit Hilfe von KI-Approximationstechniken mit akzeptabler Genauigkeit zu reduzieren. Die nächste Herausforderung besteht darin, ressourceneffiziente Techniken (Inferenz-Compiler) zu entwickeln, um das komprimierte Modell auf eine geeignete Hardwareplattform abzubilden, z. B. Low-End-FPGAs oder eingebettete (KI-) Mikrocontroller, unter Berücksichtigung der Ressourcennutzung in Bezug auf Fläche, Leistung/Energie und Latenz/Durchsatz, wie in Abbildung 1 dargestellt.

Bezug zum Thema Data ScienceDie Bewertung und Anwendung von KI/ML-Methoden im Bereich "Machine Vision", z.B. der Einsatz von CNNs in der Objektklassifizierung, sind ein Kernthema der Data Science und werden beispielsweise in den Modulen "Data Mining & Machine Learning" und "Artificial Intelligence" behandelt. KI-gestützte Bildverarbeitung stellt hohe Anforderungen an die Organisation und Verarbeitung von Daten auf allen Ebenen von IoT-Verarbeitungskonzepten (Edge/Fog/Cloud). Dies ist der Kern des Moduls "Big Data

Architekturen". Die Betrachtung des gesamten Systemprozesses vom bildgebenden Sensor bis in die Cloud erfordert eine ganzheitliche Betrachtung des gesamten Data-Science-Prozesses, die im Modul "Data Science" behandelt wird.

Verfügbare RessourcenSicherstellung der Verfügbarkeit von Daten, Rechenressourcen, Hardware, Anwendungsexperten

- Die für die Erstellung des Szenarios erforderlichen Informationen (Systembeschreibung, Schnittstellen, Dokumentation, relevante Kennzahlen etc.) werden bereitgestellt

- Steinel GmbH stellt umfangreiche Testdatensätze aus realen Produktionsumgebungen zur Verfügung

- Der Ansprechpartner der Steinel GmbH steht Ihnen für die Dauer des Projekts zur Verfügung

- Die für die Prototypenentwicklung benötigten Komponenten sowie weitere benötigte Materialien werden von der Steinel GmbH zur Verfügung gestellt

- Hardware für das komplexere maschinelle Lernen steht über das Data Science Lab, das CfADS und den KI-Rechencluster yourAI an der Hochschule Bielefeld zur Verfügung

Erstes Semester: Erstellung eines Forschungsexposés als Prüfung. Vertrautheit mit dem Konzept KI-basierter Objekterkennungsalgorithmen, insbesondere YOLO, R-CNN, Bilderkennung, Approximationstechniken für neuronale Netze, Hardwareplattformen und Design-Flow-Tools.

Zweites Semester: Erstellung des Systemkonzepts zur Entwurfsraumexploration von kognitiven EdgeComputing-Architekturen. Recherche zu relevanten Arbeiten auf dem Gebiet der KI-basierten Objekterkennungsalgorithmen und der Modellkomprimierung im oben genannten Kontext. Erstellung einer Arbeit, die einen Überblick über das jeweilige Forschungsgebiet gibt, als Prüfungsleistung.

Drittes Semester: Entwicklung eines ersten Demonstrators und Proof-of-Concept zur Hardwarebeschleunigung für Human Presence Detector (HPD) mit z.B. YOLO-V7. Vergleich des entwickelten Frameworks mit einer klassischen Implementierung.

Viertes Semester: Masterarbeit und Kolloquium. Implementierung und Vergleich verschiedener Kombinationen von KI-basierten Objekterkennungsalgorithmen und Hardwarebeschleunigern. Systematische Bewertung und Untersuchung der Effizienz des entwickelten Rahmens. Abschließende Bewertung durch Vergleich der implementierten Strategien mit den modernsten Methoden. Erstellung einer Arbeit mit den ersten quantitativen Ergebnissen als Prüfung.

EignungskriterienZwingend:

- Gute Kenntnisse in Python, Pytorch

- Gute Kenntnisse von C++

Optional:

- Erfahrung mit Hardware-Design-Flow-Tools

- Programmierung von Mikrocontrollern/FPGAs

- Grundkenntnisse in HDL (Verilog, VHDL)

- Erfahrung mit IoT-Geräten

- Erfahrung mit dem Versionskontrollsystem "git".

- Ressourceneffiziente Informationsverarbeitung am Edge (eingebettete Mikrocontroller,

FPGAs) im Einklang mit dem IoT-Verarbeitungskonzept

- Sensorbezogene Informationsverarbeitung

- AI/ML-basierte Objekterkennungsmethoden

- Nutzung von eingebetteter Hardware zur Beschleunigung von AI/ML-Prozessen